- Регистрация

- 17 Февраль 2018

- Сообщения

- 25 397

- Лучшие ответы

- 0

- Баллы

- 2 093

Offline

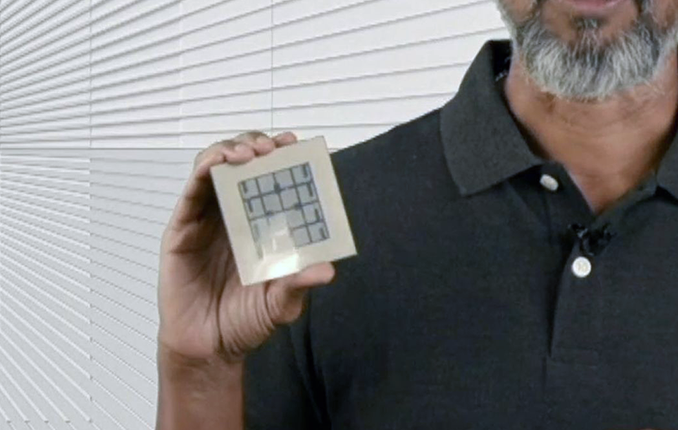

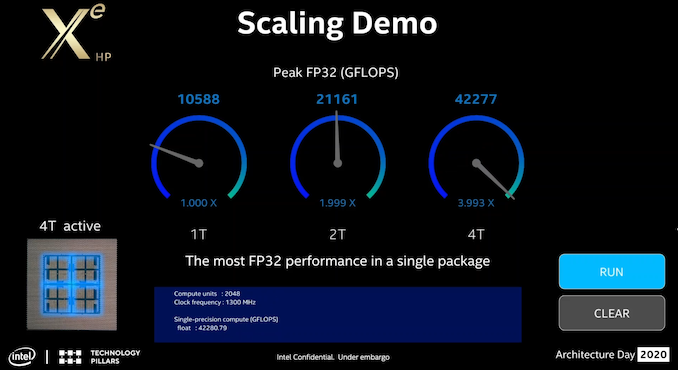

At last week’s Intel Architecture Day, Intel’s chief architect, Raja Koduri, briefly held up the smallest member of the company’s forthcoming Xe-HP series of server CPUs, the one tile configuration. Now, only a few days later, he has upped the ante by showing off the largest, four tile configuration.

Designed to be a scalable chip architecture, Xe-HP is set to be available with one, two, or four tiles. And while Intel has yet to disclose too much in the way of details on the architecture, based on their packaging disclosures it looks like the company is using their EMIB tech to wire up the GPU tiles, as well as the GPU’s on-package HBM memory.

Assuming it makes it to market, a multi-tiled GPU – essentially multiple GPUs in a single package – would be a major accomplishment for Intel. GPUs are notoriously bandwidth-hungry due to the need to shovel data around between cores, caches, and command frontends, which makes them non-trivial to split up in a chiplet/tiled fashion. Even if Intel can only use this kind of multi-tile scalability for compute workloads, that would have a significant impact on what kind of performance a single GPU package can attain, and how future servers might be built.